研究内容RESEARCHES

Smart Vision & Robotic Sensing

高速ビジョン・ロボットセンシング

- >> 研究テーマ

- 1秒間に1000コマ以上の実時間画像処理を実現する高速ビジョン技術を始めとして、人間の感覚能力を遥かに上回る実時間センシング技術の確立を目指した情報システム/デバイスの研究開発を行うとともに、高速化・集積化を念頭においたアルゴリズムの研究、さらには人間には感じとることが難しい振動ダイナミクス等の情報を積極的利用した新たなセンシング技術の実現を目指します。

CFPEビジョンチップ

|

|

|

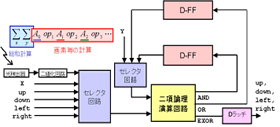

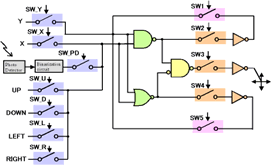

CFPEアーキテクチャでは、(1)再帰的処理による画素局所演算の実現、(2)画素局所演算と総和演算の回路共通化、(3)ダイナミック回路などによる回路要素のコンパクト化という3つの設計方針に基づき、記憶回路や制御信号に対する入力信号選択回路を可能な限りコンパクト化し、処理の汎用性をある程度保った上で、画素ディジタル回路面積の大幅な縮小化を実現した。

設計したビジョンチップアーキテクチャについて、画素毎の処理ブロックを右上図、ゲートレベルで記述したものを右中図に示す。これらの回路アーキテクチャは、膨張・収縮操作11.6ns、エッジ検出11.6ns、対象追跡13.6ns、オイラー数55μs(いずれも256×256画素時)などの各種2値画像処理が高速に動作することをシミュレーションにより確認した。

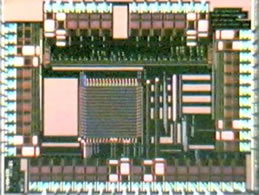

本アーキテクチャに基づき、0.35μm CMOSプロセスを用いた16×16画素試作チップ(2.5mm×2.0mm)の開発を行った。 試作チップは画素回路規模が40トランジスタ、画素サイズが33μm×33μmとなった。この回路規模に基づくとCFPEアーキテクチャに基づくビジョンチップとして、1cm角におよそ100,000画素程度を集積可能である。

参考文献

- 山本健吉, 窪園宗寛, 石井抱 : 高解像度ビジョンチップのためのCFPEアーキテクチャ, 電子情報通信学会論文誌D, Vol.J89-D, No.1, pp.56-63 (2006)

- Kenkichi Yamamoto, Munehiro Kubozono, and Idaku Ishii: Development of High-resolution Digital Vision Chip Based on CFPE Architecture, Proc. IEEE Int. Workshop on Computer Architecture for Machine Perception and Sensing, pp.24-29, 2006.