RESEARCHES

Smart Vision & Robotic Sensing

Professor, Robotics Laboratory

Smart Innovation Program, Graduate School of Advanced Science and Engineering

Hiroshima University

Smart Innovation Program, Graduate School of Advanced Science and Engineering

Hiroshima University

Idaku ISHII

- >> Research Contents

- In order to establish high-speed robot senses that are much faster than human senses, we are conducting research and development of information systems and devices that can achieve real-time image processing at 1000 frames/s or greater. As well as integrated algorithms to accelerate sensor information processing, we are also studying new sensing methodologies based on vibration and flow dynamics; they are too fast for humans to sense.

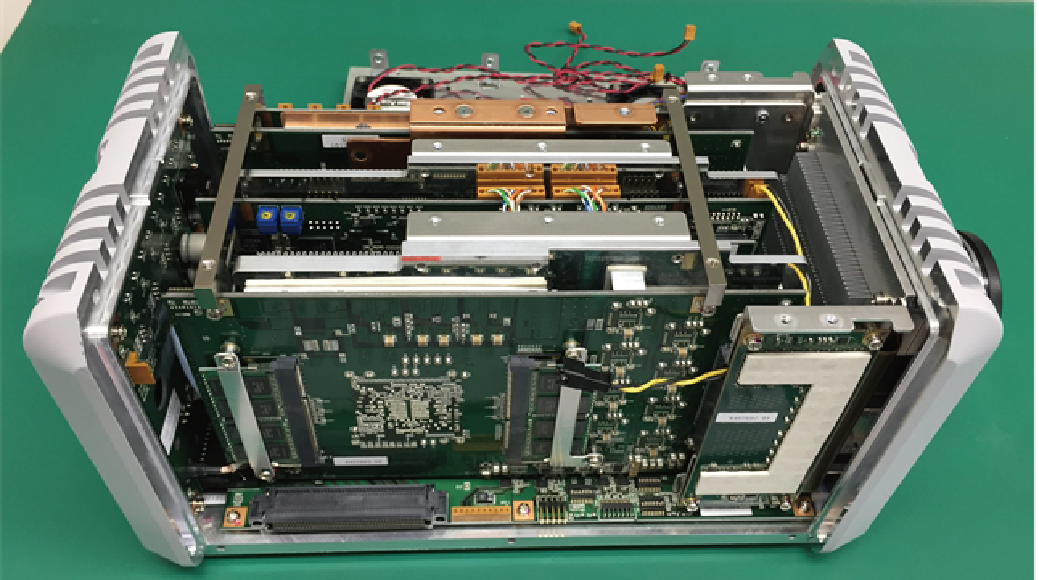

Super high-speed vision platform in real time at 12500 fps

This study describes a super high-speed vision platform (HSVP) that can process a 12-bit, gray level, 1024 x 1024 image at 12500 frames per second (fps) simultaneously by implementing parallel hardware logic on a large size field programmable gate array (FPGA) platform.

The system consists of a 1024 x 1024 CMOS image sensor with a 256 parallel analog output, 256 parallel amplifier/AD converter for converting the analog output, one FPGA for the camera parameter setting (TG FPGA), two FPGAs that incorporate image data into the memory (MEM FPGA), one FPGA which outputs the HD-SDI image for image display (DISP FPGA), one FPGA for storing image data in the SD memory (SDIF FPGA), and one FPGA which controls various types of PFGAs and connects to external devices, such as a PC through Gigabit Ethernet (GbE).

Multiple experimental results demonstrate that our platform can calculate a 4096-level brightness-histogram and 4096-level edge-intensity histogram for 1024 x 1024 images at 12500 fps, including the zeroth and first moment features for centroid calculation.

The system consists of a 1024 x 1024 CMOS image sensor with a 256 parallel analog output, 256 parallel amplifier/AD converter for converting the analog output, one FPGA for the camera parameter setting (TG FPGA), two FPGAs that incorporate image data into the memory (MEM FPGA), one FPGA which outputs the HD-SDI image for image display (DISP FPGA), one FPGA for storing image data in the SD memory (SDIF FPGA), and one FPGA which controls various types of PFGAs and connects to external devices, such as a PC through Gigabit Ethernet (GbE).

Multiple experimental results demonstrate that our platform can calculate a 4096-level brightness-histogram and 4096-level edge-intensity histogram for 1024 x 1024 images at 12500 fps, including the zeroth and first moment features for centroid calculation.

|

|

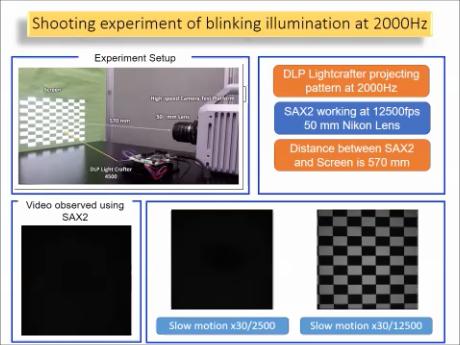

mp4 movie(7.89M) Shooting experiment of blinking illumination at 2000Hz |

|

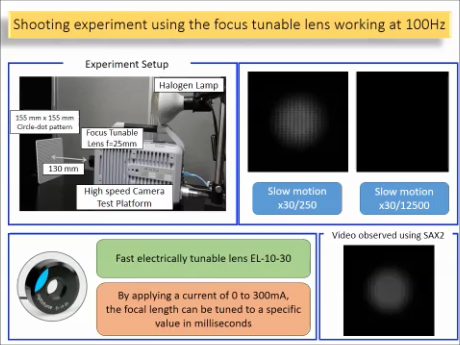

mp4 movie(4.17M) Shooting experiment using the focus tunable lens working at 100Hz |

|

mp4 movie(7.08M) Shooting experiment of rotating fan at a high speed |