研究内容RESEARCHES

Smart Vision & Robotic Sensing

高速ビジョン・ロボットセンシング

- >> 研究テーマ

- 1秒間に1000コマ以上の実時間画像処理を実現する高速ビジョン技術を始めとして、人間の感覚能力を遥かに上回る実時間センシング技術の確立を目指した情報システム/デバイスの研究開発を行うとともに、高速化・集積化を念頭においたアルゴリズムの研究、さらには人間には感じとることが難しい振動ダイナミクス等の情報を積極的利用した新たなセンシング技術の実現を目指します。

高次自己相関ビジョンチップ

|

|

用途を対象認識、特に計数機能に限定することで、高速かつ高解像度でのビジョンチップを実現した。

提案アーキテクチャでは、認識処理の画像特徴量として高次局所自己相関特徴を用い、ビジョンチップ上での

高次自己相関特徴およびモーメント演算を可能とした。

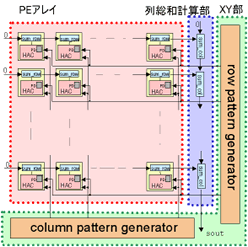

画素間の距離を参照点の3×3画素の局所近傍領域に限定した高次局所自己相関特徴は、25個の局所特徴パターンに対して高次自己相関特徴を計算することにより得られる。このようなパターン認識のための特徴量と対象位置を計算するためのモーメント特徴量を同時集積化することに特化して、設計したビジョンチップアーキテクチャを示す。

PEは相関演算を行う乗算処理部とその総和計算を行う総和部に大別され、X、Y座標生成回路より座標値情報が入力される。

本アーキテクチャは高次自己相関特徴とモーメント演算の2つの処理を同一回路上で実現可能としており、回路面積を増やすことなくその機能を高めている。

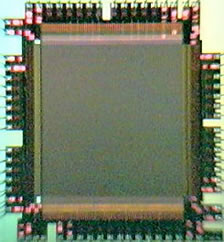

本アーキテクチャに基づき、0.35μm CMOSプロセスを用いた64×64画素試作チップ(5mm角サイズ)の開発を行った。

下図に示す試作チップは画素回路規模が73トランジスタ、画素サイズが44μm×48μmであり、1cm角に47,000画素程度を集積可能であることがわかった。また試作チップの最高総和クロック周波数は8.5MHzであり、1ミリ秒あたりに650の特徴量を抽出できる。

また試作チップを搭載した右下図の評価ボードを開発し、高速回転するドラム上に設置されたパターン形状に対する動作実験を行った。その結果、形状や大小の異なる対象の個数を500fps(この設定は露光時間によるもの)で計数できることを確認した。

|

|

|

長方形形状の計数実験 MPEG動画(2.9M) 再生 |

|

大小の円の計数実験 MPEG動画(2.9M) 再生 |

参考文献

- Idaku Ishii, Kenkichi Yamamoto, and Munehiro Kubozono : Higher Order Autocorrelation Vision Chip, IEEE Transactions on Electron Devices, Vol.53, No.8, pp.1797-1804 (2006)

- Kenkichi Yamamoto, Munehiro Kubozono, and Idaku Ishii: Development of Higher Order Autocorrelation Vision Chip, Proc. IEEE/RSJ Int. Conf. on Intelligent Robots and Systems, pp.3258-3263, 2005.

- 山本健吉, 石井抱: 高次自己相関ビジョンチップの設計, 電子情報通信学会論文誌D-II, Vol.J86-D-II, No.8, pp.1205-1211 (2003).